# **P-N JUNCTION SILICON BANDGAP ENERGY**

Last Revision: August 1, 2007

## **QUESTION TO BE INVESTIGATED:**

What is the energy difference  $E_g$  between the valence and conducting bands in a silicon p-n junction?

### **INTRODUCTION:**

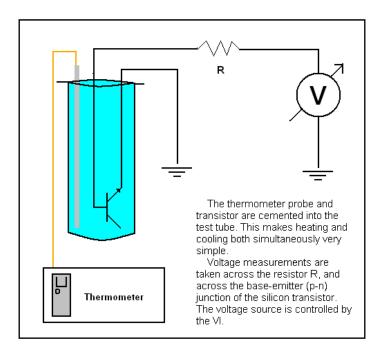

The theory and general procedure for this investigation are described in the article by Collings (Am. Jour. Phys. <u>48</u>, (1980),197), which is available on the course website. Read this first. The analysis of data and the experiment have evolved to permit measurements at a wider range of temperatures and to include nonlinear terms. A schematic diagram for the measurements is shown in Figure 1. Becoming familiar with the terminology of semiconductor physics is obviously important for a successful investigation. You may wish to consult Melissinos & Napolitano §2.4 in addition to Collings.

Figure 1: Schematic circuit diagram for the Band Gap measurement.

### <u>THEORY</u>

The diode equation, which is derived in textbooks on solid state physics or electronics, expresses the current I through a p-n junction for both signs of the applied voltage V

$$I = I_0 \left( e^{\frac{eV}{kT}} - 1 \right) \tag{1}$$

where e is the fundamental electronic charge, k is Boltzmann's constant and T is the absolute temperature. For silicon p-n junctions and positive values of V the exponential term becomes quickly greater than 1 This implies that the current through the junction will scale exponentially with V. Since kT is about 1/40th of a volt at room temperature, this will be true for applied voltages greater than a few tenths of a volt even at the lowest temperatures used in this experiment. The dependence on the energy gap occurs through the factor  $I_0$ . This is the current that flows when the junction is biased negatively and is due to the thermal excitation of electrons across the energy gap after which they flow freely across the junction. A complete treatment of the problem shows that  $I_0$  is proportional to the factor f given by

$$f \alpha T^{\frac{3}{2}} e^{\frac{-E_g}{kT}}$$

<sup>(2)</sup>

where  $E_g$  is the energy gap to be determined in this experiment. It might seem that  $I_O$  could be determined by a simple measurement with a negative bias applied to the junction. However,  $I_O$  is so small that an extremely careful measurement would be demanded to produce results with sufficient accuracy. You must generate curves representing Eq (1) at several temperatures in order to obtain several values for  $I_O$ . From these values you will be able to obtain  $E_g$  as discussed by Collings (1980). Specifically, his fourth figure.

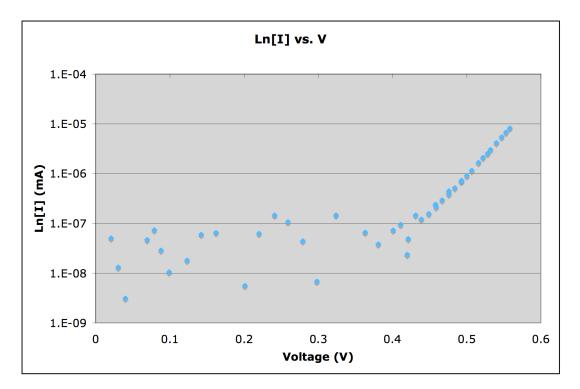

When Eq. (1) is plotted on a semi-log plot (See Figure 2) a straight line should be seen. The straight-line portion of the curve has three interesting regions. Lower, middle and upper - In the lower region you have a point where 2 things happen: the

eV/kT signal gets small enough that either the meter cannot read it, or  $I_o$  becomes dominant.

Figure 2: A sample data set. This data was taken at 21.6 °C. Note the Y-axis is logarithmic. The right-most region represents the exponential dependence of Eq (1), and on the left you can see the noise surrounding a direct measurement of Io, which is almost 0A.

The right part of the curve is the region dominated by the exponential term e<sup>eV/kT</sup>. Nonlinear effects will occur if you go too high in current due to I<sup>2</sup>R heating.

### Experiment:

As stated above, it would be incredibly difficult to take a reliable measurement of  $I_O$  from a simple negative bias. A much more reliable procedure is to measure I for a range of applied voltages, plot the logarithm Ln(I) versus V, and determine the intercept of the resulting straight line, which will be  $\text{Ln}(I_O)$ . Once  $I_O$  has been determined as a function of temperature, a plot of  $\text{Ln}(I_O)$  versus (1/T) should,

Three sources of systematic error have been identified in the straight line plots of  $\ln(I)$  vs. V. First, if the current flowing through the junction is too high, internal heating of the device will occur. This will cause the actual temperature of the junction to be higher than that measured by the sensor by an amount which depends on the current. This would be seen as a non-linearity near the top of the curve. Second, there may be contact potentials, thermal emf's and meter DC offsets which serve to add or subtract from the meter readings. This will produce nonlinearities near the low end of the curves. Poor contacts result in huge variations in the results and must be carefully soldered. Corrections may be made for contact potential errors, DC offsets and thermal emf's by adding or subtracting a constant amount to each measured value made on a given meter scale. Meter offsets will depend on the scale but should become relatively unimportant as the voltage being measured increases. Third, sufficient time might not have been allowed to let the assembly come to thermal equilibrium at the new temperature. In this case the points taken too early will not fall on the line determined by points taken after the temperature has become constant. Note the constancy of the junction current at a given bias is probably a better indication of a constant temperature than the thermometer. It would be wise to repeat a few measurements at the end of each run to check on this source of error. Note that systematic errors totally dominate this lab. One of the challenges of this experiment is to include a reasonable estimate of these effects in calculating the uncertainties in the final results.

All of the data for a single temperature should be taken in one session. It is strongly recommended that the first run be done at room temperature during the first day to verify correct operation of the equipment.

You should report:

- The values of  $E_g$  for the Silicon and Germanium semiconductors

- A sample plot of Ln(I) vs. V

- Your combined plot of  $Ln(I_0)$  vs. T<sup>-1</sup>

- Any claims and their evidence that you feel help correct for the internal systematic errors of your measurements.

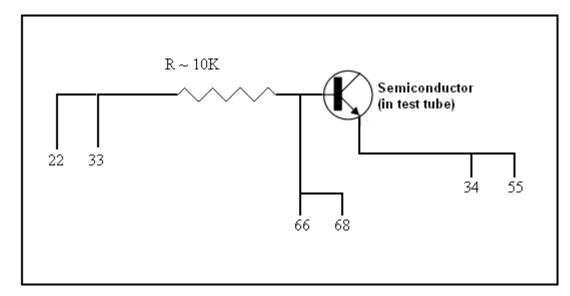

Figure 4 GPIB interface cartoon